# Microprocessadores

Família "x86" - Hardware do i8086

António M. Gonçalves Pinheiro

Departamento de Física Universidade da Beira Interior Covilhã - Portugal

pinheiro@ubi.pt

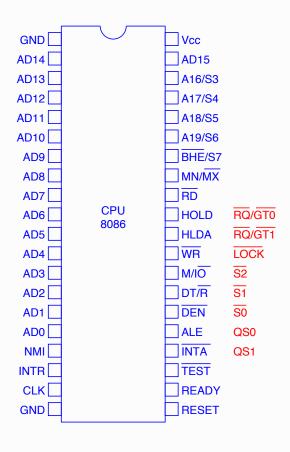

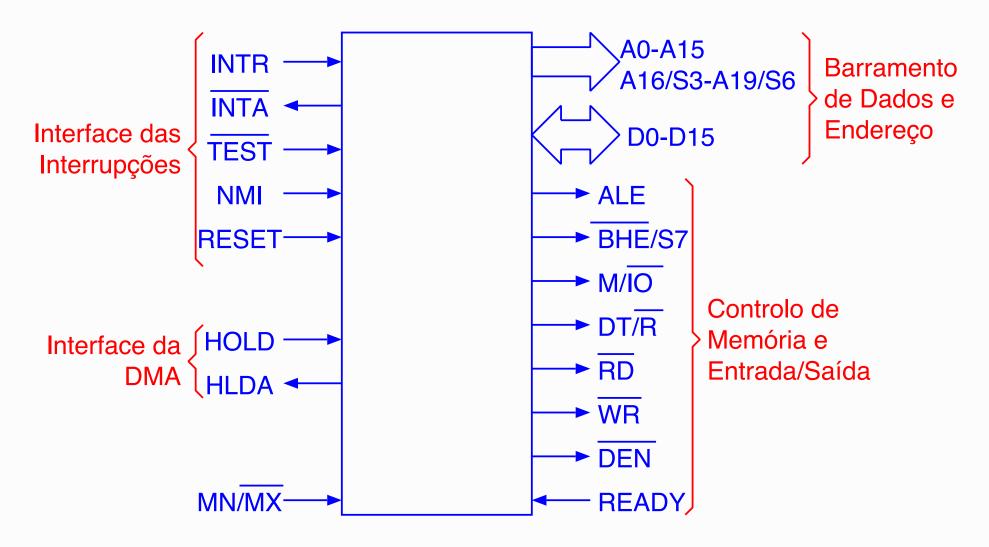

**Sinais Comuns**

| Nome          |                              |                 |

|---------------|------------------------------|-----------------|

| AD15-AD0      | Barramento de                | 3 Estados/      |

|               | Endereços/Dados              | Bidireccional   |

| A19/S6-A16/S3 | Barramento de                | 3 Estados/Saída |

|               | Endereços/Estado             |                 |

| BHE/S7        | BUS HIGH ENABLE/             | 3 Estados/Saída |

|               | Estado                       |                 |

| MN/MX         | Controlo Mínimo/Máximo       | Entrada         |

| RD            | Controlo de Leitura          | 3 Estados/Saída |

| TEST          | Controlo de Espera de Teste  | Entrada         |

| READY         | Controlo de Estado de Espera | Entrada         |

| NMI           | Non-Maskable Interrupt Rqst  | Entrada         |

| INR           | Interrupt Request            | Entrada         |

| CLK           | Relógio do Sistema           | Entrada         |

| Vcc           | +5 Volts                     | Entrada         |

| GND           | Tensão de Referência         | Entrada         |

### Sinais do Modo Mínimo $(MN/\overline{MX}=1)$

| Nome                              | Função                        | Tipo            |

|-----------------------------------|-------------------------------|-----------------|

| HOLD                              | Hold Request                  | Entrada         |

| HLDA                              | Hold Acknowledgemnet          | Saída           |

| $\overline{\mathbf{W}\mathbf{R}}$ | Controlo de Escrita           | 3 Estados/Saída |

| M/IO                              | Controlo de Memória/IO        | 3 Estados/Saída |

| DT/R                              | Transmissão/Recepção de dados | 3 Estados/Saída |

| <b>DEN</b>                        | Data Enable                   | 3 Estados/Saída |

| ALE                               | Address Latch Enable          | Saída           |

| <b>INTA</b>                       | Acknowledge de Interrupção    | Saída           |

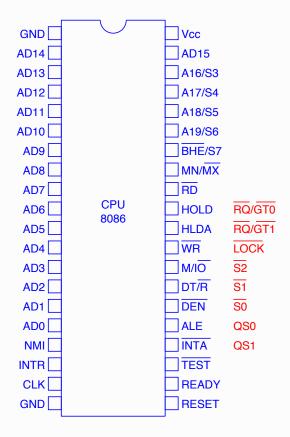

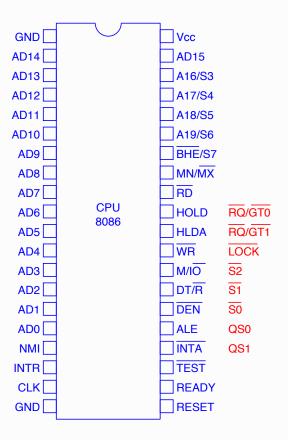

### Sinais do Modo Máximo (MN/MX=0)

| Nome                              | Função                              | Tipo            |

|-----------------------------------|-------------------------------------|-----------------|

| <b>RQ/GT</b> 1, 0                 | RQ/GT1, 0 Request/Grant de          |                 |

|                                   | Controlo de Barramento              |                 |

| <b>LOCK</b>                       | Controlo de Prioridade              | 3 Estados/Saída |

|                                   | do Barramento                       |                 |

| $\overline{S2}$ - $\overline{S0}$ | Estado do Ciclo do Barramento       | 3 Estados/Saída |

| QS1-QS0                           | Estado da Fila de Instrucções Saída |                 |

#### Diagrama de Blocos do Modo Mínimo

#### Sinais de Estado

| <b>S</b> 4 | <b>S</b> 3 | Registo de Segmento |

|------------|------------|---------------------|

| 0          | 0          | Extra               |

| 0          |            | Stack               |

| 1          | 0          | Código/Nenhum       |

| _1_        | 1          | Dados               |

#### Modo Máximo

| $\overline{S2}$ | <del>S</del> 1 | $\overline{S0}$ | Ciclo de CPU          | Comando    |

|-----------------|----------------|-----------------|-----------------------|------------|

| 0               | 0              | 0               | Interrupt Acknowledge | INTA       |

| 0               | 0              | 1               | Leitura de Porto      | IORC       |

| 0               | 1              | 0               | Escrita de Porto      | IOWC,AIOWC |

| 0               | 1              | 1               | Halt                  |            |

| 1               | 0              | 0               | Busca de Instrucção   | MRDC       |

| 1               | 0              | 1               | Leitura de Memória    | MRDC       |

| 1               | 1              | 0               | Escrita de Memória    | MWTC,AMWC  |

| 1               | 1              | 1               | Passivo               |            |

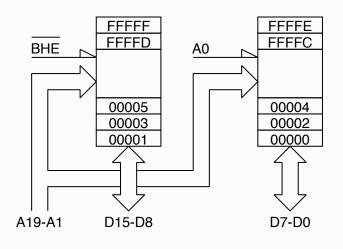

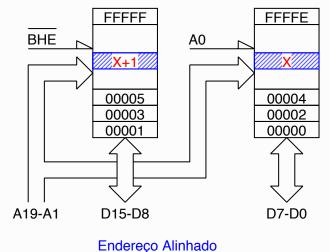

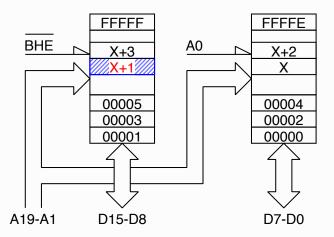

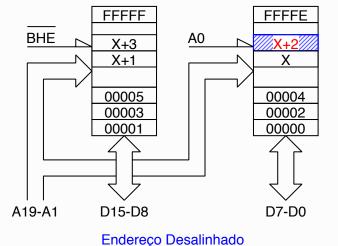

#### Acesso à Memória

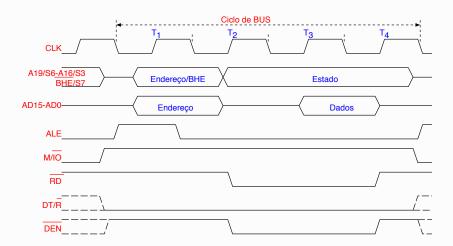

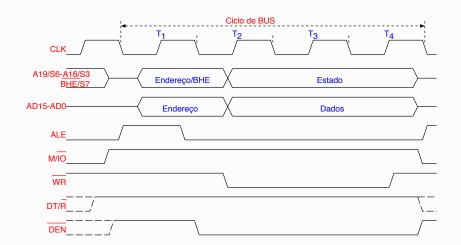

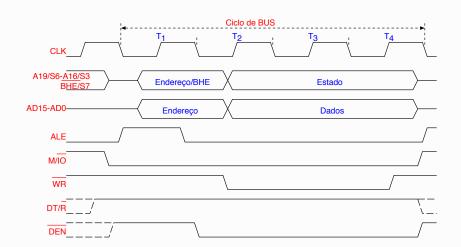

#### Ciclos de Leitura e Escrita de Memória

Ciclo de Leitura de Memória

Ciclo de Escrita de Memória

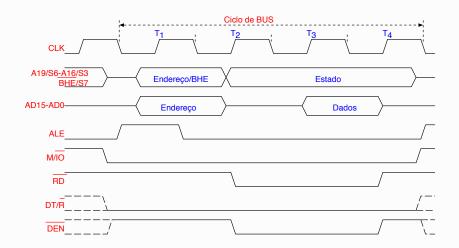

#### Ciclos de Leitura e Escrita de I/O

Ciclo de Leitura de Porto

Ciclo de Escrita de Porto

# Interrupções

| End. Mem | Entrada Tbl | Def. Vector |                          |

|----------|-------------|-------------|--------------------------|

| 3FE      | CS 255      | Vector 255  | Disponível ao Utilizador |

| 3FC      | IP 255      |             |                          |

|          |             |             |                          |

|          |             |             |                          |

|          |             |             |                          |

| 82       | CS 32       | Vector 32   | Disponível ao Utilizador |

| 80       | IP 32       |             |                          |

| 7E       | CS 31       | Vector 31   | Reservado                |

| 7C       | IP 31       |             |                          |

|          |             |             |                          |

|          |             |             |                          |

|          |             |             |                          |

| 16       | CS 5        | Vector 5    | Reservado                |

| 14       | IP 5        |             |                          |

| 12       | CS 4        | Vector 4    | Overflow                 |

| 10       | IP 4        |             |                          |

| 0E       | CS 3        | Vector 3    | Breakpoint               |

| 0C       | IP 3        |             |                          |

| 0A       | CS 2        | Vector 2    | NMI                      |

| 08       | IP 2        |             |                          |

| 06       | CS 1        | Vector 1    | Single-Step              |

| 04       | IP 1        |             |                          |

| 02       | CS 0        | Vector 0    | Divide Error             |

| 00       | IP 0        |             |                          |

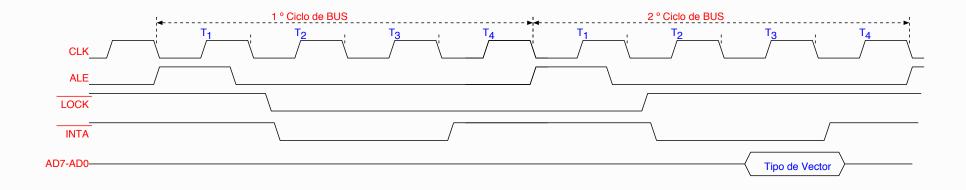

### "Ciclo de Acknowledgment" de Interrupção